# **IP Datasheet**

#### StreamDSP LLC

20 S Third St, Suite 210 Columbus, OH 43215 USA (855) DSP-FPGA http://www.streamdsp.com

email: sales@streamdsp.com

## **Serial FPDP**

for Altera, Xilinx, and Microsemi FPGAs

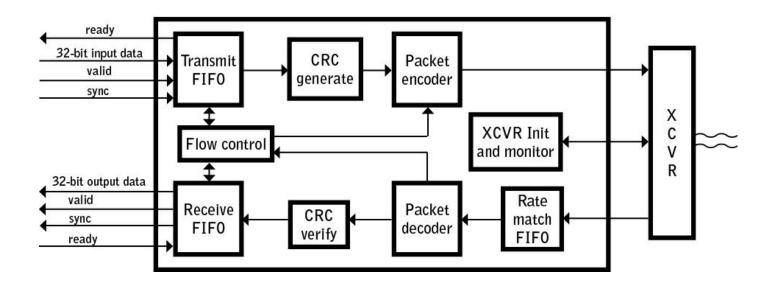

Serial Front Panel Data Port is an industry standard, low-overhead, low-latency, high speed serial communications protocol. sFPDP is ideal for use in applications such as high-speed communication system backplanes, high-bandwidth remote sensor systems, signal processing, data recording, and high-bandwidth video systems. The simple and lightweight nature of the protocol makes it an attractive choice for replacement of parallel bus interconnects using serial transceiver technology. sFPDP can be used in point-to-point or loop topologies, unidirectional or bi-directional links, and easily supports different types of data with efficient and flexible data framing options.

StreamDSP is committed to performance, efficiency, and flexibility. Our sFPDP core is unique in that we support nearly all transceiver based devices from Altera and Xilinx as well as Microsemi Igloo-2 devices. We're always making improvements to the core with innovative new features such as multi-lane bonding for increased bandwidth, and we're continually updating the core to support new transceiver based devices offered by Altera, Xilinx, and Microsemi. Our core provides a open interface to the FPGA transceiver. giving the user complete control over transceiver speed, settings and adjustments. A complete reference design is provided for each family, as well as a thorough testbench with support for Aldec's Active-HDL and Riviera-Pro as well as Mentor's ModelSim tools. In addition, our testing procedure includes exhaustive interoperability testing among all FPGA families and manufacturers to ensure compatibility.

StreamDSP is committed to delivering the highest level of customer support to ensure smooth system integrations. We also offer IP core customization and FPGA design services.

### **Features**

- ☑ VITA 17.1-2003 Compliant

- ☑ Conforms to FC-PH disparity rules

- ✓ Multi-lane channel bonding wrapper

- ☑ Independent data / system clock domains

- ☑ 600 Mbps to 10+ Gbps serial rate support

- ✓ Optional flow control and CRC

- ☑ 32-bit user data interface

- ☑ Basic control/status interface

- ☑ Unidirectional and bidirectional support

- ☑ Optional link startup "junk filtering"

- ☑ All sFPDP frame types supported

- Unframed data

- Single frame data

- Fixed size repeating frame data

- Dynamic size repeating frame data

- ☑ All sFPDP system configurations

- Basic System

- Flow Control

- Bidirectional Data Flow

- Copy Mode

- Copy/Loop Mode

# **IP Datasheet**

StreamDSP LLC

20 S Third St, Suite 210 Columbus, OH 43215 USA (855) DSP-FPGA http://www.streamdsp.com

email: sales@streamdsp.com

# **Details**

### **Resource Usage**

| Registers | LUTs | *RAM      |

|-----------|------|-----------|

| 772       | 841  | 14 Blocks |

\* RAM size dependent on user controlled TX and RX FIFO depths

### Throughput (per lane)

| Line Rate  | Throughput |  |

|------------|------------|--|

| 2.5 Gbps   | 247 MB/s   |  |

| 4.25 Gbps  | 420 MB/s   |  |

| 5.0 Gbps   | 494 MB/s   |  |

| 6.375 Gbps | 630 MB/s   |  |

| 8.5 Gbps   | 841 MB/s   |  |

| 10.0 Gbps  | 990 MB/s   |  |

### **Delivery Options**

HDL Language: **VHDL** License Types:

- Netlist

- Source Code

- \* Free, supported evaluations available on request

# **IP Datasheet**

StreamDSP LLC

20 S Third St, Suite 210 Columbus, OH 43215 USA (855) DSP-FPGA

http://www.streamdsp.com

email: sales@streamdsp.com

## **Details**

### **FPGA Family Support**

#### **ALTERA**

#### **Example Design**

Cyclone-IV GX Altera Cyclone-IV GX Starter Kit Cyclone-V GX/SX Arrow Cyclone-V SoCkit Arria GX Altera Arria-GX PCIe Dev Kit Arria-II GX Altera Arria-II GX PCIe Dev Kit Arria-II GZ Full working TB and example designs Arria-V GX Altera Arria-V GX Starter Kit Arria-V GZ Full working TB and example designs Arria-10 GX Altera Arria-10 Development Board Stratix-II GX Altera Stratix-II GX PCIe Dev Kit Stratix-IV GX Altera Stratix-IV GX PCIe Dev Kit Stratix-V GX Altera Stratix-V GX PCIe Dev Kit

#### **XILINX**

Virtex-2 Pro Custom Hardware board Spartan-6 LXT Xilinx SP605 Development Kit Kintex-7 Xilinx KC705 Evaluation Kit Virtex-4 FX Xilinx ML405 Development Kit Virtex-5 LXT Xilinx ML555 Development Kit Virtex-5 FXT Xilinx ML507 Development Kit Virtex-6 LXT Xilinx ML605 Development Kit Virtex-7 GTX Xilinx VC707 Evaluation Kit Virtex-7 GTH Xilinx VC709 Evaluation Kit Artix-7 Xilinx AC701 Development Kit Xilinx KCU105 Development Kit Kintex-UltraScale Virtex-UltraScale Full working TB and example designs Zynq-7000 Xilinx ZC706 Development Kit

#### **MICROSEMI**

• Igloo-2 Microsemi Igloo-2 Evaluation Kit

All deliveries include VHDL and Verilog simulation models, a self-checking testbench with simulation scripts, and ready-to-run design targeted at a popular development board for each family (listed above).